# VQFN48

**Layout Hints**

VQFN48-15, -19, -20, -22, -24, -48, -51, -52, -53, -54, -55, -56, -57 VQFN48-29, -31

# **Application Note**

Rev. 1.0, 2012-12-01

# **Automotive Power**

# **Table of Contents**

**Revision History** 7

6

| 1   | Abstract 1                                             |  |  |

|-----|--------------------------------------------------------|--|--|

| 2   | Introduction 2                                         |  |  |

| 3   | Layout Suggestion for VQFN48 Packages 3                |  |  |

| 3.1 | Packages with Tie Bars 3                               |  |  |

| 3.2 | Recommendation for a Layout with Respect to Tie Bars 4 |  |  |

| 4   | Conclusion 5                                           |  |  |

| 5   | Additional Information 6                               |  |  |

Application Note 1 Rev. 1.0, 2012-12-01

**Abstract**

### 1 Abstract

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

This Application Note is intended to provide a specific information what to consider when creating a **P**rinted **C**ircuit **B**oard (PCB) Layout containing an integrated circuit in a VQFN48 package. This Application Nore applies to the following package variants:

VQFN48-15, -19, -20, -22, -24, -48, -51, -52, -53, -54, -55, -56, -57 VQFN48-29, -31

Application Note 1 Rev. 1.0, 2012-12-01

Introduction

## 2 Introduction

Besides designing rules and layout requirements originating from electromagnetic compliance also package related issues should be accounted for. This Application Notes gives an indication and suggestion what has to be considered when designing a layout of a PCB with an integrated circuit using specific VQFN48 packages with tie bars.

Application Note 2 Rev. 1.0, 2012-12-01

**Layout Suggestion for VQFN48 Packages**

## 3 Layout Suggestion for VQFN48 Packages

### 3.1 Packages with Tie Bars

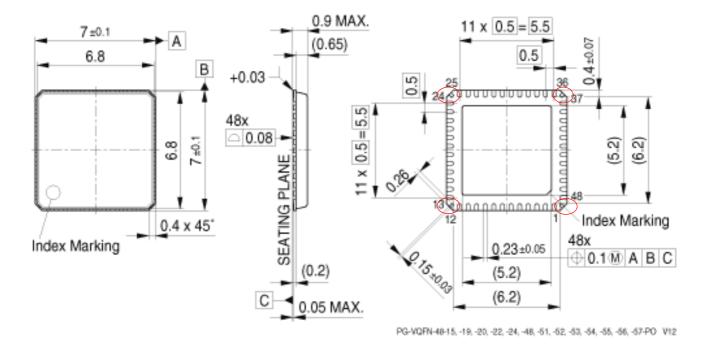

The P(G)-VQFN, Plastic (Green) Very Thin Profile Quad Flat Non Leaded Package (see **Figure 1**) is a near chip-scale plastic encapsulated package. It provides on the package bottom side perimeter pads and also a large die exposed pad, which is typically also soldered to the printed circuit board to get an optimum of electrical and thermal performance and board level reliability. "**G**" **denotes** "**green**" **VQFN packages**, **which means lead-free package material set (RoHS compliant).**

#### **Features**

- Optimized electrical performance with short leads

- Enhanced thermal performance through exposed die pad structure

- · Leads and exposed die pad with solder plating

- · Small footprint, thin package

- Package outline according JEDEC MO-220

For further recommendations for Printed Circuit Board (PCB) assembly of VQFN packages see the Infineon Additional Information: "Recommendations for Printed Circuit Board Assembly of Infineon P(G)-VQFN Packages, DS7, May 2012".

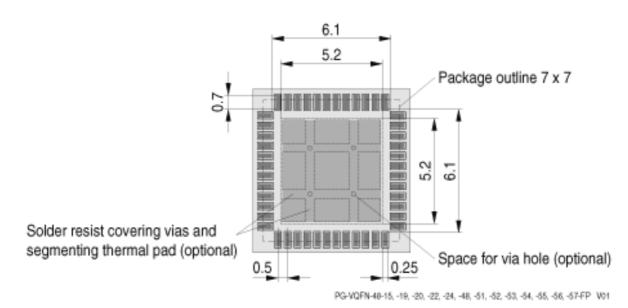

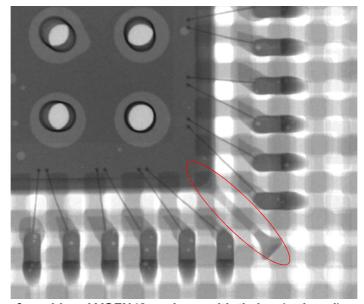

This Applications Note focuses on the PCB Layout with specific attention to the tie bars. The packages VQFN48-15, -19, -20, -22, -24, -48, -51, -52, -53, -54, -55, -56, -57 and VQFN48-29, -31 have visible tie bars on each corner which are connected to the lead frame (see **Figure 1** red circles). In **Figure 3** (Source: "**Recommendations for Printed Circuit Board Assembly of Infineon P(G)-VQFN Packages, DS7, May 2012**") it can be seen that the lead frame is connected to the exposed pad and thus most likely connected to GND.

Figure 1 Engineering drawing of the VQFN48 package outline.

Application Note 3 Rev. 1.0, 2012-12-01

#### **Layout Suggestion for VQFN48 Packages**

Figure 2 Engineering drawing of the VQFN48 package footprint.

Figure 3 X-ray image of a soldered VQFN48 package with tie bar (red oval).

### 3.2 Recommendation for a Layout with Respect to Tie Bars

The layout and routing of trace pitches on a PCB close to tie bars has to be evaluated accurately with respect to the corresponding application and requirements. To prevent the tie bars from establishing shorts to any elements on the PCB it is required to ensure the isolation of any conducting elements (i.e. vias, resistors, circuits with no solder resist, ...). It needs to be ensured that no shorts are possible on the PCB to any conducting element.

Application Note 4 Rev. 1.0, 2012-12-01

Conclusion

## 4 Conclusion

The not masked tie bars are originating from the production process and have no specific functionality. The tie bars are not pins and are located in the corners of the package. It needs to be ensured in the application that there is no short between the tie bars and vias, wires or other conducting elements.

Application Note 5 Rev. 1.0, 2012-12-01

**Additional Information**

# **5** Additional Information

For further information you may contact <a href="http://www.infineon.com/">http://www.infineon.com/</a>

Application Note 6 Rev. 1.0, 2012-12-01

**Revision History**

# 6 Revision History

| Revision | Date       | Changes          |

|----------|------------|------------------|

| 1.0      | 2012-04-12 | Initial Revision |

|          |            |                  |

|          |            |                  |

Application Note 7 Rev. 1.0, 2012-12-01

Edition 2012-12-01

Published by Infineon Technologies AG 81726 Munich, Germany © 2012 Infineon Technologies AG All Rights Reserved.

#### **LEGAL DISCLAIMER**

THE INFORMATION GIVEN IN THIS APPLICATION NOTE IS GIVEN AS A HINT FOR THE IMPLEMENTATION OF THE INFINEON TECHNOLOGIES COMPONENT ONLY AND SHALL NOT BE REGARDED AS ANY DESCRIPTION OR WARRANTY OF A CERTAIN FUNCTIONALITY, CONDITION OR QUALITY OF THE INFINEON TECHNOLOGIES COMPONENT. THE RECIPIENT OF THIS APPLICATION NOTE MUST VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE REAL APPLICATION. INFINEON TECHNOLOGIES HEREBY DISCLAIMS ANY AND ALL WARRANTIES AND LIABILITIES OF ANY KIND (INCLUDING WITHOUT LIMITATION WARRANTIES OF NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS OF ANY THIRD PARTY) WITH RESPECT TO ANY AND ALL INFORMATION GIVEN IN THIS APPLICATION NOTE.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.